Материалы по тегу: risc-v

|

27.12.2024 [13:44], Сергей Карасёв

Стартап Ubitium создал универсальный чип на базе RISC-V с функциями CPU, GPU, DSP и FPGAСтартап Ubitium, основанный в 2024 году, анонсировал проект по созданию чипа с универсальной архитектурой, которая полностью независима от рабочих нагрузок. Речь идёт об объединении в одном изделии решений разного типа: CPU, GPU, DSP и FPGA. Отмечается, что на протяжении более 50 лет полупроводниковая промышленность занималась созданием самостоятельных центральных, графических и других процессоров, предназначенных для решения конкретных вычислительных задач. Ubitium предлагает пересмотреть данный подход, создав универсальный чип на открытой архитектуре RISC-V, который сможет одинаково хорошо справляться с нагрузками разного типа. Стартап отмечает, что основным препятствием для внедрения новых процессоров являются проприетарные ISA, которые требуют использования специализированных программных инструментов. Кроме того, трудности может создавать отсутствие зрелой программной экосистемы, предоставляющей необходимые фреймворки и приложения. Чипы Ubitium, как утверждается, будут на 100 % совместимы с RISC-V, что упростит и ускорит разработку и внедрение конечных продуктов. В отличие от традиционных процессоров со специализированными ядрами, предназначенными для определённых задач, блоки универсального чипа Ubitium могут динамически «переназначаться» для обработки широкого спектра вычислительных нагрузок, включая простую логику управления, общие вычисления, ИИ и рендеринг графики. Ещё одним преимуществом предлагаемой концепции стартап называет масштабируемость. Ubitium планирует выпускать изделия разного уровня, которые при этом будут иметь идентичную архитектуру и использовать одни и те же программные инструменты. Компания рассчитывает, что её чипы смогут применяться в самых разных сферах — от встраиваемых устройств, бытовой электроники и домашней техники до систем промышленной автоматизации, роботов и космического оборудования. По сравнению с традиционными процессорами, использование решений Ubitium, как утверждается, обеспечит повышение гибкости, снижение стоимости и ускорение разработки. Компания заявляет, что универсальный чип может обеспечить в 10–100 раз большую производительность в расчёте на доллар по сравнению с современными специализированными решениями. В команду Ubitium входят выходцы из Intel, NVIDIA и Texas Instruments. Головной офис компании находится в Дюссельдорфе (Германия). Генеральным директором является Хён Шин Чо (Hyun Shin Cho) из Университета Пердью (Purdue University). Пост технического директора занимает Мартин Форбах (Martin Vorbach), на имя которого зарегистрированы более 200 патентов. Стартап Ubitium уже привлёк $3,7 млн начального финансирования. На данный момент компания создала экспериментальную эмуляцию, которая подтверждает, что универсальный процессор работоспособен. Первые коммерческие решения планируется выпустить к 2026 году.

27.12.2024 [12:40], Сергей Карасёв

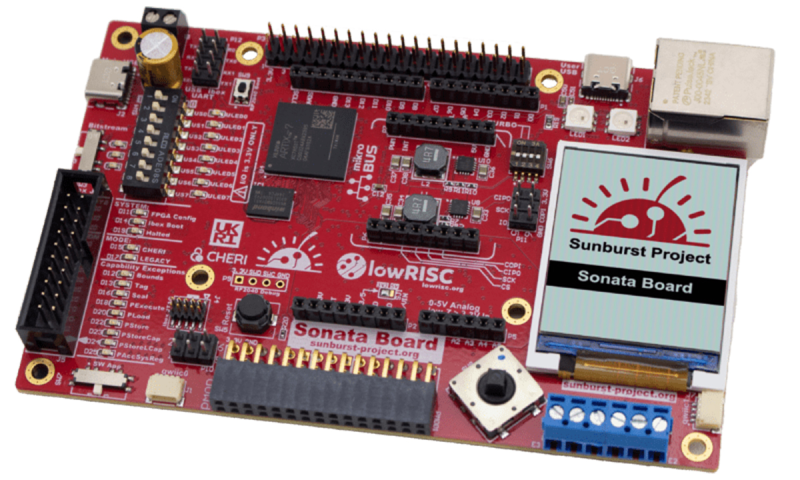

Плата lowRISC Sonata v1.0 с системой защиты памяти CHERIoT объединяет FPGA AMD Artix-7 и микроконтроллер Raspberry Pi RP2040Участники проекта lowRISC по созданию 64-бит чипов RISC-V, как сообщает ресурс CNX Software, анонсировали аппаратную платформу Sonata v1.0 для разработчиков встраиваемых систем и всевозможных устройств Интернета вещей (IoT). Новинка поддерживает технологию CHERIoT (Capability Hardware Extension to RISC-V for IoT). Напомним, летом уходящего года lowRISC, а также Capabilities Limited, Codasip, FreeBSD Foundation, SCI Semiconducto и Кембриджский университет создали альянс CHERI для продвижения средств надёжной защиты памяти от атак. Специальные механизмы исключают ряд потенциальных уязвимостей, таких как переполнение буфера или некорректная работа с указателями. Отмечалось, что первыми новую технологию могут получить процессоры RISC-V. В основе платформы Sonata v1.0 лежит FPGA AMD Xilinx Artix-7 (XC7A35T-1CSG324C). Изделие содержит Soft-процессорное ядро AMD MicroBlaze с архитектурой RISC и 400 Кбайт распределённой памяти RAM. Ещё одной составляющей платы является микроконтроллер Raspberry Pi RP2040 (два ядра Cortex-M0+ с частотой 133 МГц), который отвечает за IO-функции. Есть 64 Мбит памяти HyperRAM (Winbond W956D8MBYA5I), 256 Мбит памяти SPI-флеш (Winbond W25Q256JVEIQ) для FPGA AMD Artix-7 или Raspberry Pi RP2040, ещё 64 Мбит SPI-флеш (Winbond W25Q64JVZEIQ) для RP2040 и 256 Мбит памяти SPI-флеш (Winbond W25Q256JVEIQ) для FPGA. В арсенале Sonata v1.0 — встроенный цветной ЖК-дисплей с диагональю 1,8″, сетевой порт 10/100MbE, два разъёма USB Type-C (для программирования и подачи питания) и слот microSD. Реализованы последовательные интерфейсы RS-232 и RS-485, 40-контактный разъём Raspberry Pi, две 10-контактные колодки Ibex JTAG, две 4-контактные колодки Ibex UART и пр. Размеры составляют 125 × 80 мм. Разработчики могут получить доступ к подробной документации и дополнительным ресурсам на сайтах lowRISC и GitHub, чтобы в полной мере использовать возможности платформы Sonata v1.0. Цена новинки — примерно $413.

26.12.2024 [11:35], Сергей Карасёв

Индийский RISC-V-стартап Mindgrove привлек на развитие $8 млнИндийский стартап Mindgrove Technologies, занимающийся разработкой SoC для различных сфер применения, провёл раунд финансирования Series A, в ходе которого на развитие привлечено $8 млн. Деньги будут направлены на ускорение вывода продуктов на коммерческий рынок. Фирма Mindgrove основана в 2021 году. Штаб-квартира располагается в исследовательском парке Мадрасского технологического института (IITM) в Ченнаи. Компания не имеет собственных производственных мощностей: она занимается проектированием изделий под брендом Mindgrove Silicon.

Источник изображения: Mindgrove Mindgrove фокусируется на чипах для вычислений общего назначения. Речь идёт о решениях для таких отраслей, как автомобилестроение, робототехника, носимые гаджеты и интеллектуальные устройства. В частности, в мае 2024 года Mindgrove анонсировала чип Secure IoT — первую в Индии высокопроизводительную коммерческую SoC, для которой предусмотрена 28-нм технология производства. Изделие предназначено для смарт-часов, умных счётчиков и замков, принтеров, POS-терминалов и пр. Чип, как ожидается, выйдет на рынок к середине 2025 года. Кроме того, Mindgrove проектирует процессор на открытой архитектуре RISC-V, ориентированный на камеры видеонаблюдения, видеорегистраторы, автомобильные системы помощи водителю (ADAS) и смарт-телевизоры. В начале 2023 года Mindgrove Technologies получила $2,325 млн начального финансирования от Peak XV Partners (ранее Sequoia Capital India & SEA), Speciale Invest и Whiteboard Capital. Новый инвестиционный раунд на $8 млн возглавили Rocketship.vc и Speciale Invest при участии Mela Ventures, Peak XV Partners, Nishchay Goel, Whiteboard Capital и Anshul Goel. Полученные средства будут направлены на расширение штата, улучшение инженерных возможностей и коммерциализацию продуктов.

24.12.2024 [15:41], Сергей Карасёв

Sipeed выпустила NanoKVM-PCIe — плату расширения IP-KVM с OLED-дисплеем и Wi-Fi 6Компания Sipeed анонсировала решение NanoKVM-PCIe — плату расширения с интерфейсом PCIe для организации удалённого управления IP-KVM (Keyboard, Video, Mouse). Изделие может применяться в настольных рабочих станциях, а также в стоечных серверах. Новинка представляет собой альтернативу крошечному модулю NanoKVM, вышедшему летом нынешнего года. В основу NanoKVM-PCIe положен чип Sophgo SG2002, который объединяет два ядра C906 с архитектурой RISC-V (1000 и 700 МГц), одно ядро Arm Cortex-A53, а также контроллер 8051 с частотой от 25–300 МГц. Есть нейропроцессорный блок с производительностью до 1 TOPS (INT8) и 256 Мбайт памяти DDR3. Карта располагает слотом microSD, интерфейсом HDMI с поддержкой видео 1080p60, сетевым портом 10/100MbE RJ45 с опциональной поддержкой PoE, а также двумя разъёмами USB Type-C. Дополнительно в оснащение может быть включён адаптер Wi-Fi 6 с коннектором для антенны. Особенность NanoKVM-PCIe заключается в наличии небольшого информационного OLED-дисплея с диагональю 0,49″ и разрешением 64 × 32 точки: этот экран расположен на монтажной планке. Плата имеет низкопрофильное исполнение с габаритами 66 × 57 × 18 мм. Питание (0,2 A / 5 В) может подаваться через слот PCIe, порт USB Type-C или посредством PoE. Применяется прошивка с поддержкой управления UEFI/BIOS, эмулированными USB-мышью/клавиатурой и USB-накопителем, IPMI, WoL, Tailscale, WebSSH и пр. компания Sipeed принимает предварительные заказы на новинку по цене от $42 до $58 в зависимости от выбранных опций.

17.12.2024 [11:50], Сергей Карасёв

Вышла крошечная плата Pico W5 с контроллером Raspberry Pi RP2350, Wi-Fi 4 и Bluetooth 5.0По сообщению ресурса CNX Software, в продажу поступила микроплата Pico W5, построенная на контроллере Raspberry Pi RP2350. Изделие может стать альтернативой устройству Raspberry Pi Pico 2 W, которое дебютировало менее месяца назад. Чип RP2350 содержит по два ядра Arm Cortex-M33 и RISC-V Hazard3 с тактовой частотой 150 МГц. Однако использовать их одновременно нельзя: нужная пара ядер выбирается при инициализации платы. Объём встроенной памяти SRAM составляет 520 Кбайт. Реализована функция Secure Boot (только при использовании блока Arm). Новинка несёт на борту 8 Мбайт памяти QSPI Flash. В оснащение входят адаптеры Wi-Fi 4 802.11n (частотные диапазоны 2,4 и 5 ГГц) и Bluetooth 5.0 (LE) на основе модуля BW16 (контроллер Realtek RTL8720DN). Предусмотрен порт USB Type-C 1.1.

Источник изображения: CNX Software Крошечная плата Pico W5 располагает 26 контактами GPIO с поддержкой 2 × UART, 2 × SPI, 2 × I2C, 24 × PWM, 4 × ADC. Габариты составляют 51 × 21 мм, масса — 3 г. Питание (5 В) подаётся через коннектор USB Type-C. Диапазон рабочих температур простирается от -10 до +60 °C. Модель Pico W5 поддерживает разработку на базе Arduino и MicroPython. Приобрести новинку можно по ориентировочной цене $7. Столько же стоит оригинальная версия Raspberry Pi Pico 2 W, но это изделие поддерживает Wi-Fi 802.11n только в диапазоне 2,4 ГГц.

01.12.2024 [11:25], Сергей Карасёв

Плата Milk-V Megrez формата Mini-ITX с чипом RISC-V и NPU-модулем стоит $200В продажу поступила компактная плата Milk-V Megrez, предназначенная для построения систем на архитектуре RISC-V. Новинка ориентирована в первую очередь на разработчиков: говорится о поддержке таких фреймворков, как PyTorch, TensorFlow, PaddlePaddle, ONNX и пр. Изделие выполнено в форм-факторе Mini-ITX с размерами 170 × 170 мм. Применён процессор ESWIN EIC7700X: он содержит четыре ядра SiFive P550 (RV64CG) с тактовой частотой до 1,8 ГГц. Встроенный графический блок Imagination AXM-8-256 обладает поддержкой OpenGL ES 3.2, EGL 1.4, OpenCL 1.2/2.1 EP2, Vulkan 1.2. В состав чипа входит нейропроцессорный узел (NPU) с производительностью 19,95 TOPS в режиме INT8 и 9,975 TOPS в режиме INT16. Milk-V Megrez может нести на борту 8, 16 или 32 Гбайт оперативной памяти LPDDR5-6400 (впаяна на плату). Есть коннекторы M.2 для SSD с интерфейсом SATA-3 и eMMC для флеш-модуля, слот для карты microSD и порт SATA-3. Предусмотрен также слот PCIe х8 (PCIe 3.0 x4): возможна, в частности, установка ускорителя AMD 7900 XTX. В оснащение включены двухпортовый сетевой контроллер 1GbE и разъём M.2 E-Key для адаптера беспроводной связи. Для вывода изображения служит интерфейс HDMI 2.0. Заявлена возможность декодирования видеоматериалов H.265 8K@50р и кодирования H.265 up to 8K@25р. Доступны четыре порта USB 3.0 Type-A, два гнеза RJ-45 для сетевых кабелей, аудиовход и аудиовыход на 3,5 мм. Питание (12 В) может подаваться через DC-разъём. Цена платы варьируется от $200 до $270 в зависимости от объёма ОЗУ.

26.11.2024 [10:05], Сергей Карасёв

Вышла крошечная плата Raspberry Pi Pico 2 W за $7 с поддержкой Wi-Fi и Bluetooth 5.2Компания Raspberry Pi представила микроконтроллерную плату Pico 2 W — улучшенную версию Pico 2, дебютировавшей в августе нынешнего года. Новинка обзавелась поддержкой беспроводной связи Wi-Fi 802.11n (2,4 ГГц) и Bluetooth 5.2, которая отсутствует у оригинала. Анонсированная плата построена на микроконтроллере RP2350, объединяющем по два ядра Arm Cortex-M33 и RISC-V Hazard3 с тактовой частотой 150 МГц. Одна из двух пар ядер выбирается при инициализации устройства — использовать одновременно блоки Arm и RISC-V нельзя. В состав чипа входят 520 Кбайт памяти SRAM. Модель Pico 2 W несёт на борту 4 Мбайт флеш-памяти. Реализована поддержка 2 × UART, 2 × SPI, 2 × I2C, 24 × PWM, 3 × ADC. Кроме того, присутствует порт Micro-USB 1.1. Использовать плату можно при температурах от -20 до +85 °C. Диапазон входных напряжений — от 1,8 до 5,5 В.

Источник изображения: Raspberry Pi Новинка на программном и аппаратном уровнях совместима с Raspberry Pi Pico 1. Упомянута поддержка средств безопасности TrustZone для кластера Arm-ядер. Отмечается, что в целом архитектура безопасности RP2350, включая защищённую загрузочную область, подробно документирована и доступна всем пользователям без каких-либо ограничений. Программирование может осуществляться на C/C++ и Python. По заявлениям Raspberry Pi, плата Pico 2 W подходит как энтузиастам, так и профессиональным разработчикам, создающим решения на открытой платформе RISC-V. Новинку можно приобрести за $7, тогда как вариант без Wi-Fi и Bluetooth обойдётся в $5. Изделие предлагается по отдельности и в катушках по 480 модулей для промышленного использования.

19.11.2024 [11:47], Сергей Карасёв

Esperanto и NEC займутся созданием HPC-решений на базе RISC-VСтартап Esperanto Technologies и корпорация NEC объявили о заключении соглашения о сотрудничестве в области НРС. Речь идёт о создании программных и аппаратных решений следующего поколения, использующих открытую архитектуру RISC-V. Напомним, Esperanto разрабатывает высокопроизводительные RISC-V-чипы для задач НРС и ИИ. Первым продуктом компании стало изделие ET-SoC-1, которое объединяет 1088 энергоэффективных ядер ET-Minion и четыре высокопроизводительных ядра ET-Maxion. Решение предназначено для инференса рекомендательных систем, в том числе на периферии. В августе 2023 года стало известно о подготовке чипа ET-SoC-2 с высокопроизводительными ядрами RISC-V с векторными расширениями. В рамках соглашения о сотрудничестве, как отмечается, будут объединены опыт и экспертизы NEC в области проектирования суперкомпьютеров и создания специализированного софта для HPC-задач с технологиями Esperanto в сфере высокопроизводительных энергоэффективных чипов на основе набора инструкций RISC-V. При этом упоминаются достижения NEC по направлению векторных процессоров: японская компания проектировала уникальные изделия SX-Aurora, но их разработка была остановлена в 2023 году.

Источник изображения: Esperanto «Используя глубокий опыт и экспертные знания NEC в области HPC, а также открытый набор инструкций RISC-V в сочетании с вычислительной технологией Esperanto, мы сможем разрабатывать масштабируемые и эффективные решения для ИИ и высокопроизводительных вычислений», — отметил Арт Свифт (Art Swift), президент и генеральный директор Esperanto.

25.10.2024 [13:24], Сергей Карасёв

От тостера до ЦОД: RISC-V International ратифицировала унифицированный профиль RVA23 для процессоров будущегоОрганизация RISC-V International объявила о ратификации профиля RVA23. Это значимое событие, которое, как ожидается, поможет открытой архитектуре RISC-V укрепить позиции по отношению к Arm и x86, избегая при этом потенциальных проблем, связанных с лицензированием. Профили RVA необходимы для обеспечения переносимости ПО между различными аппаратными реализациями. Таким образом, разработчики софта могут избежать привязки к конкретному поставщику аппаратных решений. Иными словами, одно и то же приложение сможет функционировать на любых устройствах, оснащённых процессорами с архитектурой RISC-V. Профиль RVA23 стандартизирует набор инструкций ISA (Instruction Set Architecture). Ключевой задачей является устранение фрагментации внутри экосистемы RISC-V. Отмечается, что в рамках ратификации профиль RVA23 прошёл длительный процесс разработки, рассмотрения и утверждения в многочисленных рабочих группах.

Источник изображения: pixabay.com RVA23 делает обязательными такие функции, как векторные операции, инструкции с плавающей запятой и атомарные инструкции, которые необходимы во многих сферах, включая НРС, машинное обучение и ИИ. В частности, векторные расширения ускоряют рабочие нагрузки с интенсивными математическими расчётами, включая криптографию, (де-)компрессию, обучение ИИ и пр. Важным компонентом RVA23 является поддержка гипервизоров. Это позволяет виртуализировать корпоративные рабочие нагрузки как на локальных серверах, так и в облаке. Таким образом, может быть ускорена разработка оборудования, ОС и прикладных программ для архитектуры RISC-V. Поддержка виртуализации также улучшит безопасность мобильных приложений путём разделения защищённых и незащищённых компонентов.

25.10.2024 [00:35], Игорь Осколков

NVIDIA за год отгрузила более 1 млрд RISC-V ядерВ рамках саммита RISC-V 2024 компания NVIDIA поделилась любопытной статистикой — за год в составе GPU и других ускорителей она отгрузила более 1 млрд ядер RISC-V собственной разработки, передаёт TechPowerUp. Они входят в состав GSP (GPU System Processor), который отвечает за управление GPU и иные служебные функции. В состав GSP входит от 10 до 40 ядер, в зависимости от сложности чипа, которым он управляет. Компания переключилась на разработку нового GSP на базе RISC-V в 2016 году. До этого более десяти лет NVIDIA использовала для GSP проприетарный процессор Falcon, возможностей и гибкости которого со временем стало не хватать. Вместо покупки и доработки готовых ядер от сторонних вендоров (Arm, MIPS, Synopsys ARC) или попыток улучшить Falcon, компания решила обратиться к открытой архитектуре RISC-V и к настоящему моменту разработала три типа ядер. Так, NV-RISCV32 представляет собой самое простое 32-бит ядро без внеочередного исполнения, работающее на частоте до 1,8 ГГц и имеющее производительность до 1,8 CoreMark/МГц. NV-RVV является NV-RISCV32 с 1024-бит векторными расширениями. А NV-RISCV64 — это уже более серьёзное 64-бит ядро с поддержкой внеочередного исполнения и SMP, частотой 2 ГГц и производительностью 5 CoreMark/МГц. Кроме того, NVIDIA разработала более 20 расширений ISA под специфические задачи. Впервые GSP на базе RISC-V появился в поколении Turing в 2018 году. Сейчас GSP отвечает за управление питанием и ресурсами ускорителя, безопасность, межчиповое взаимодействие, управление видеокодеками, вывод видео, работу с NVDLA и т.д. Google выбрала похожий путь — в её ИИ-ускорителях TPU используются ядра SiFive. Впрочем, сейчас есть уже и «большие» ИИ-ускорители, построенные исключительно на ядрах RISC-V: Meta✴ MTIA первого и второго поколений, InspireSemi Thunderbird, Tenstorrent Wormhole и Grayskull, а также Esperanto ET-SoC-1 и ET-SoC-2. |

|